DS90CF363BMT/NOPB

DS90CF363BMT/NOPB特征• 时钟/数据和/PD引脚之间无需特殊的启动顺序。输入信号 2(时钟和数据)可以在器件上电之前或之后施加。• 支持高达 100KHz 的扩频时钟频率调制和 ±2.5% 中心扩频或 −5% 下扩频的偏差。• 当输入时钟缺失且/PD引脚为逻辑高电平时,“输入时钟检测”功能将把所有LVDS对拉至逻辑低电平。• 支持18至68MHz移位时钟 • TxINPUT上一流的设置和保持时间 • Tx功耗< 130 mW (典型值) @65MHz灰度 • 功耗比BiCMOS同类产品低40%• Tx省电模式 < 37μW (典型值) • 支持 VGA、SVGA、XGA 和双像素 SXGA。• 窄总线减小了电缆尺寸和成本 • 高达 1.3 Gbps 的吞吐量 • 高达 170 兆字节/秒的带宽• 345mV(典型值)摆幅LVDS器件,实现低EMI • PLL无需外部元件 • 兼容 TIA/EIA-644 LVDS 标准 • 扁平 48 引脚 TSSOP 封装 • 改进了以下替代方法:– SN75LVDS84、DS90CF363A

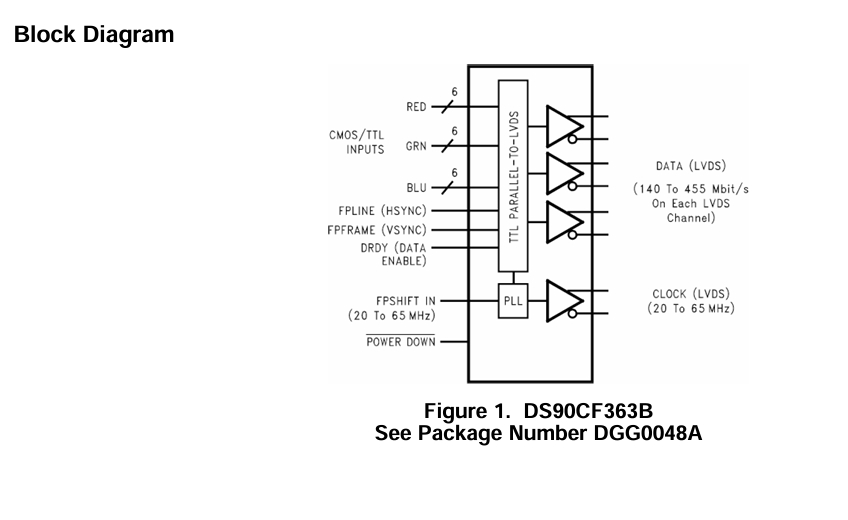

DS90CF363BMT/NOPB变送器将 21 位 CMOS/TTL 数据转换为三个 LVDS(低压差分信号)数据流。锁相发送时钟通过第四个LVDS链路与数据流并行传输。发送时钟的每个周期对 21 位输入数据进行采样和传输。在65 MHz的传输时钟频率下,每个LVDS数据通道以455 Mbps的速率传输18位RGB数据和3位LCD定时和控制数据(FPLINE、FPFRAME、DRDY)。使用 65 MHz 时钟时,数据吞吐量为 170 MB/秒。DS90CF363BMT/NOPB固定为落沿选通发射器,可与落沿选通接收器(DS90CF366)互操作,无需任何转换逻辑。该芯片组是解决与宽高速 TTL 接口相关的 EMI 和电缆尺寸问题的理想手段。

附件下载

上一篇:

ADS7846E/2K5下一篇:

TPS65185RSLRCopyright 2005-2019 深圳市利特斯电子科技有限公司 版权所有 备案号:粤ICP备18031876号-1